Datasheet Summary

3.3V LVPECL/HSTL to HSTL 1:9 HighPerformance Clock Driver with LVTTL

Clock Select and Enable

General Description

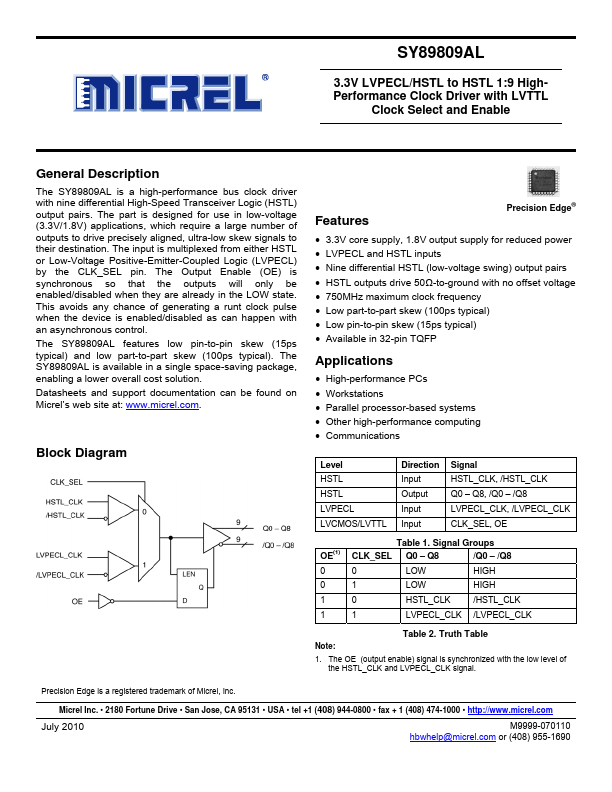

The SY89809AL is a high-performance bus clock driver with nine differential High-Speed Transceiver Logic (HSTL) output pairs. The part is designed for use in low-voltage (3.3V/1.8V) applications, which require a large number of outputs to drive precisely aligned, ultra-low skew signals to their destination. The input is multiplexed from either HSTL or Low-Voltage Positive-Emitter-Coupled Logic (LVPECL) by the CLK_SEL pin. The Output Enable (OE) is synchronous so that the outputs will only be enabled/disabled when they are already in the LOW state. This avoids any...